-

Notifications

You must be signed in to change notification settings - Fork 1

DART Edge AI

Welcome to the DART Edge AI wiki!

DART Edge AI Low-level Language.

The Initial main Branch upload consisted of a test with ChatGPT. Having not the hardware and OS desired to Prototype Embedding Characters in the Silicon Components, ChatGPT was able to emulate the materials for Prototyping - countering the lack of budget as well the current optimal production necessity being on the road at the time of this report.

The DART Edge AI Low-level Language is designed for custom Hardware Embedding. With this in place The language will assume machine code or bytecode runs from wall power across the CPU and GPU using electron states for switching gates but here where the former 0 and 1 are no longer accounted for as mathematical order of operations and radical order of operations. Instead the Language will assume there is circuit, chip, memory and any other hardware are processing the standard binary electrical current where each of the radical side of the 12 order of operations, being the last 6 operations half of the twelve, are each composed of materials that all the binary electrical pulse to trigger each of the six physics gate entirely pure pulse or binary state. This method will account for one instruction having multiple processing paths from one binary pulse. Each physic hardware unit can apply the same pulse as it's own physics independently or as a desired group and whole. The capability is due to the assumption the material which makes each physic unit has the neutrons aligned as that physic and each alignment of the 6 physics will have one additional alignment in common, the square.

In the brief the advanced future form of this manufacturing process will allow the user to narrow inquiries or programming statements to nothing more than mere checks and checkboxes of 2 variations as well as anything else explicitly desired for receiving a result.

Milestones:-:

Milestone 1: The final rule draft by spring of 2024.

Milestone 2: A working DARTEdge AI IDE geared towards Apple Hardware With the option for emulating using Cpp. Summer 2024.

Milestone 3: Opensource and Custom Hardware with DARTEdge AI for protyping after builds. Winter 2024.

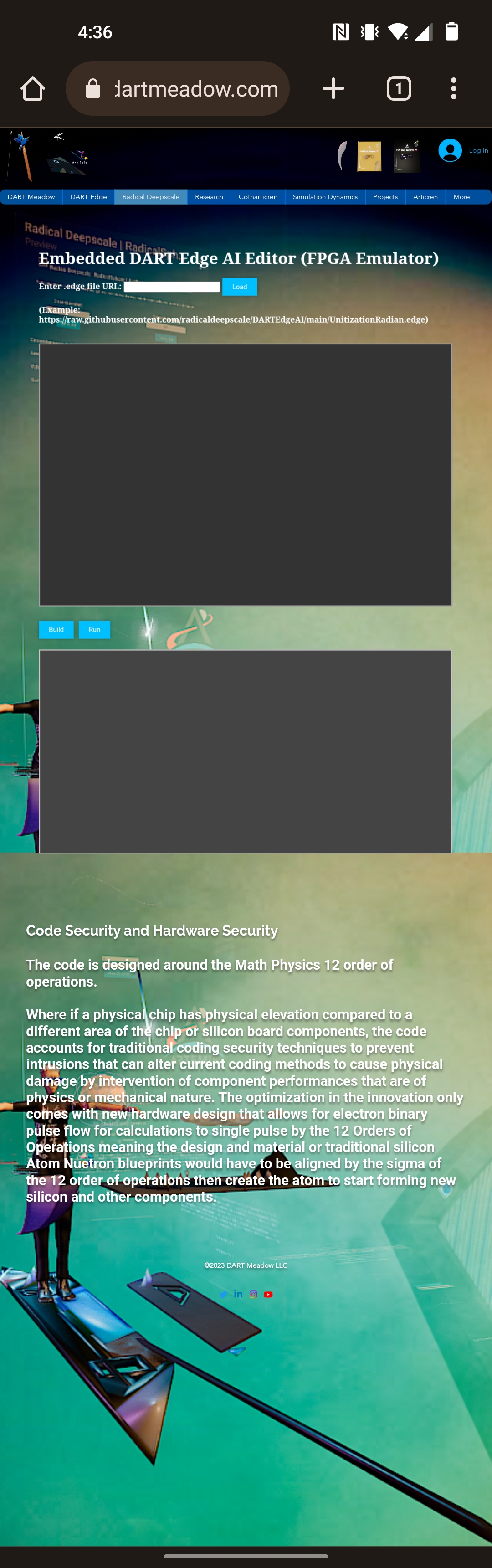

Current Embedded DART Edge AI FPGA Emulator IDE Status:

The Editor Pulls a Github Raw URL JavaScript for character syntax checking against a syntax rule set separately. The rule blocks are intended to be accessed with java much like comparing variables then build and execute can be performed. However this needs some work. Please Note that the DARTEdgeAI .edge language is intended for custom silicon material and components of appropriately measured Nuetron Blueprints.

Chief Engineer,

Justin C. Venable

Chief Executive Officer

DART Meadow LLC

Radical Deepscale LLC

https://www.dartmeadow.com/ https://www.dartedge.com/ https://www.dartedgeai.com/

Maintenance Link: https://cotharticren.wixsite.com/dartmeadow

1213 N Kingshighway Suite 102 Cape Girardeau, Missouri, 63701

©️ 2023 DART Meadow LLC and Radical Deepscale LLC Twitter@DARTMeadow